3月份,Intel、台积电、三星、日月光、AMD、ARM、高通、Google、微软、Meta(Facebook)等行业巨头联合,推出了全新的通用芯片互联标准——UCle。

几乎同一时间,中国芯片厂商芯动科技(Innosilicon)宣布,率先推出国产自主研发的物理层兼容UCIe国际标准的IP解决方案“Innolink Chiplet”,是国内首套跨工艺、跨封装的Chiplet连接解决方案。

根据芯动科技官方最新消息,该方案已经在先进工艺上量产验证成功!

Chiplet(小芯片/芯粒)技术的核心是多芯粒(Die-to-Die)互联,利用更短距离、更低功耗、更高密度的芯片裸Die间连接方式,突破单晶片(monolithic)的性能和良率瓶颈,降低大规模芯片的开发时间、成本、风险,实现异构复杂高性能SoC的集成,满足不同厂商的芯粒之间的互联需求,达到产品的最佳性能和长生命周期。

Intel、AMD、NVIDIA、苹果等新品巨头都有了此类产品,台积电等代工厂商也在推进相关工艺技术,但实现路径、技术标准各不相同。

UCIe标准就是把它们统一起来,实现不同IP芯粒之间的高速互联,将芯片设计公司、EDA设计厂商、代工厂商、封测厂商等上下游产业链联合在一起。

芯动科技称,自己在Chiplet技术领域积累了大量的客户应用需求经验,并且和台积电、Intel、三星、美光等业界领军企业有密切的技术沟通和合作探索,两年前就开始了Innolink的研发工作,率先明确Innolink B/C基于DDR的技术路线,2020年首次向业界公开Innolink A/B/C技术。

Innolink的物理层与UCIe的标准保持一致,成为国内首发、世界领先的自主UCIe Chiplet解决方案。

Innolink Chiplet的设计思路和技术特点:

1、业界很多公司认为,Chiplet跨工艺、跨封装的特性,会使其面临复杂的信号衰减路径,所以普遍使用SerDes差分技术以应对这一问题。

芯动科技则认为,相较于SerDes路线,DDR技术更适合Chiplet互联和典型应用,而且不同封装场景需要用到不同的DDR技术方案,为此提供基于GDDR6/LPDDR5技术的高速、高密度、高带宽连接方案。

2、Chiplet互连在短距PCB、基板、中介层上连接时,路径短、干扰少、信号完整性好,采用DDR技术路线在延时功耗、带宽密度上更具优势。

3、标准封装使用MCM传统基板作为Chiplet互联的介质,成本低特点,是对成本较为敏感的Chiplet应用场景首选;Interposer中介层等先进封装具备密度高、良品率低、成本高等特点,是对价格不敏感的高性能应用场景首选。

UCIe定义正式发布前,Innolink-B/C就提前实现了这两种封装场景的应用,验证了对市场前景和Chiplet技术趋势的准确判断。

4、针对长距离PCB、线缆的Chiplet连接,Innolink-A提供基于SerDes差分信号的连接方案,以补偿长路径的信号衰减。

5、总的来看,Innolink-A/B/C实现了跨工艺、跨封装的Chiplet量产方案,同时还提供封装设计、可靠性验证、信号完整性分析、DFT、热仿真、测试方案等整套解决方案。

图中显示UCIe分为三个层次,分别是Protocol Layer协议层、die to die Adapter互联层、Physical Layer物理层,其中协议层就是常用的PCIE、CXL等上层协议,底层的Die to Die和PHY物理层,则是和Innolink同样的实现方式。

最后是Innolink Chiplet内部实现的基础技术:

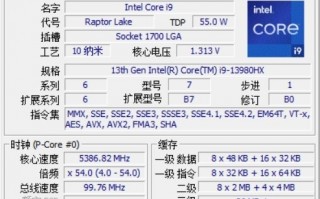

18Gbps GDDR6单端信号量产验证

21Gbps PAM4 DQ眼图

HBM3 6.4Gbps高速眼图

全球首个GDDR6/6X combo IP量产

32/56G SerDes眼图

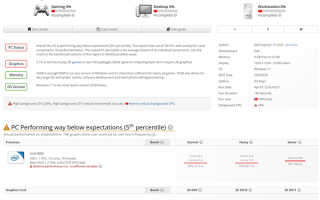

风华1号4K高性能GPU应用Innolink Chiplet实现性能翻倍

先进封装信号完整性分析

封装热效应仿真

去年11月底,芯动科技正式发布了国产显卡GPU——“风华1号”,面向桌面、服务器市场,分别是中国第一款支持4K高性能信创的桌面显卡GPU、中国第一款服务器级显卡GPU,实现了两大应用场景从0到1的突破。

它实现了国产显卡的多个第一,比如第一次渲染能力达到5-10TFlops,第一次图形API达到OpenGL 4.0以上并能实际演示Benchmark,第一次支持多路渲染+编解码+AI服务,第一次支持硬件虚拟化和chiplet可延展,等等。

风华1号的架构授权来自Imagination,而且会持续合作,持续获得授权。

如需转载请务必注明出处:快科技

责任编辑:上方文Q文章纠错

话题标签:芯动科技芯片国产